|

Prusa MINI Firmware overview

|

|

Prusa MINI Firmware overview

|

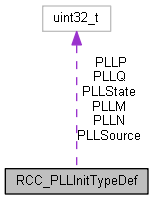

RCC PLL configuration structure definition. More...

#include <stm32f4xx_hal_rcc_ex.h>

Public Attributes | |

| uint32_t | PLLState |

| uint32_t | PLLSource |

| uint32_t | PLLM |

| uint32_t | PLLN |

| uint32_t | PLLP |

| uint32_t | PLLQ |

RCC PLL configuration structure definition.

| uint32_t RCC_PLLInitTypeDef::PLLState |

The new state of the PLL. This parameter can be a value of PLL Config

| uint32_t RCC_PLLInitTypeDef::PLLSource |

RCC_PLLSource: PLL entry clock source. This parameter must be a value of PLL Clock Source

| uint32_t RCC_PLLInitTypeDef::PLLM |

PLLM: Division factor for PLL VCO input clock. This parameter must be a number between Min_Data = 0 and Max_Data = 63

| uint32_t RCC_PLLInitTypeDef::PLLN |

PLLN: Multiplication factor for PLL VCO output clock. This parameter must be a number between Min_Data = 50 and Max_Data = 432 except for STM32F411xE devices where the Min_Data = 192

| uint32_t RCC_PLLInitTypeDef::PLLP |

PLLP: Division factor for main system clock (SYSCLK). This parameter must be a value of PLLP Clock Divider

| uint32_t RCC_PLLInitTypeDef::PLLQ |

PLLQ: Division factor for OTG FS, SDIO and RNG clocks. This parameter must be a number between Min_Data = 2 and Max_Data = 15